# Transistors et portes logiques

On explique dans cette partie le fonctionnement schématique d'un transistor ainsi que la façon de réaliser des portes logiques avec des transistors.

#### Semi-conducteurs

Les trois semi-conducteurs utilisés dans la fabrication des composants électroniques sont les suivants :

- le silicium si utilisé majoritairement,

- le germanium Ge,

- l'arséniure de gallium AsGa.

En plaçant ces différents éléments dans la table des éléments chimiques (cf. figure ci-dessous), on constate que ces éléments sont proches. Ces semi-conducteurs sont formés d'éléments ayant 4 électrons de valence sur la dernière couche comme le silicium ou le germanium ou d'un mélange d'éléments ayant 3 et 5 électrons de valence comme le gallium et l'arsenic.

| <b>B</b> 3 5   | <b>C</b> 4 6   | <b>N</b> 5 7   |  |

|----------------|----------------|----------------|--|

| Bore           | Carbone        | Azote          |  |

| <b>AI</b> 3 13 | <b>Si</b> 4 14 | <b>P</b> 5 15  |  |

| Aluminium      | Silicium       | Phosphore      |  |

| <b>Ga</b> 3 31 | <b>Ge</b> 4 32 | <b>As</b> 5 33 |  |

| Gallium        | Germanium      | Arsenic        |  |

Une partie de la table des éléments

#### Semi-conducteur intrinsèque

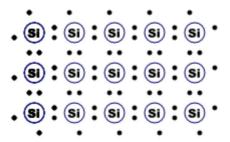

Dans un cristal de silicium pur, les atomes forment 4 liaisons de covalence avec 4 voisins. Il remplissent ainsi la dernière couche en partageant les électrons.

Cristal de silicium

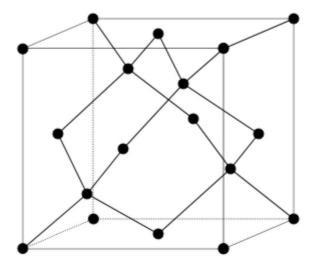

Dans la figure ci-dessus, le cristal est représenté en plan mais il faut bien sûr imaginer ce cristal dans l'espace. La maille élémentaire du réseau est représentée à la figure ci-dessous.

Réseau dans l'espace

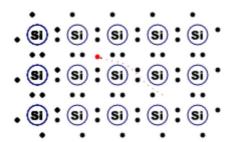

Au zéro absolu, c'est-à-dire à la température 0°K, la structure du cristal est stable et le silicium n'est pas conducteur du courant électrique. Lorsque la température augmente, les électrons possèdent une énergie supplémentaire qui provoque la rupture de certaines liaisons de covalence. Certains électrons deviennent libres (cf. figure ci-dessous) et le silicium est alors peu conducteur, d'où le nom de *semi-conducteur*.

Électron libre

#### Semi-conducteurs dopés

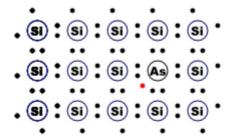

Le silicium est *dopé* en introduisant des impuretés dans le cristal. On distingue deux types de dopage suivant la nature des éléments ajoutés au silicium. On parle de semi-conducteur *de type n* (pour négatif) lorsque le dopage est réalisé avec des éléments ayant 5 électrons de covalence comme le phosphore, l'arsenic et l'antimoine. L'atome avec 5 électrons de covalence forme 4 liaisons de covalence et garde un électron qui est alors relativement libre (cf. figure cidessous).

Silicium dopé n avec un électron libre

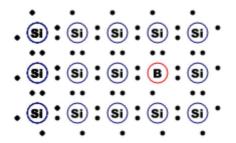

On parle de semi-conducteur *de type p* (pour positif) lorsque le dopage est réalisé avec des éléments ayant 3 électrons de covalence comme le bore, l'aluminium et le gallium. L'atome avec 3 électrons de covalence ne peut former que 3 liaisons de covalence. Il y en quelque sorte un trou d'électron (cf. figure ci-dessous).

Silicium dopé p avec un trou

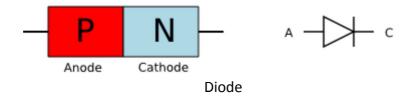

### Diode

Une jonction entre un semi-conducteur de type n et un semi-conducteur de type p est appelée une *diode*. La partie de type n est appelée *cathode* et la partie de type p est appelée *anode*. Le courant électrique ne peut passer à travers une diode que dans un seul sens comme l'évoque son symbole en forme d'entonnoir.

Le principe de fonctionnement de la diode est le suivant. Les électrons libres du semi-conducteur de type n ont tendance à aller boucher les trous du semi-conducteur de type p. Il en découle une diffusion des électrons de la région dopée n vers la région dopée p. Chaque électron qui se déplace laisse un ion positif dans la région n. Il s'ensuit donc un champ électrique de rappel vers la région n qui conduit à un équilibre. Dans cet équilibre, il y a une zone, appelée zone de charge d'espace qui ressemble à du silicium non dopé et où il y a en outre un champ électrique.

Si on applique une tension positive à la cathode et négative à l'anode, les électrons sont attirés vers le bord de la cathode et les trous vers le bord de l'anode. La zone de charge d'espace s'étend et la diode n'est pas conductrice. Si on contraire, on applique une tension positive à l'anode et négative à la cathode qui est supérieure au champ à l'équilibre, les électrons peuvent circuler de la cathode vers l'anode et la diode est conductrice.

### **Transistors**

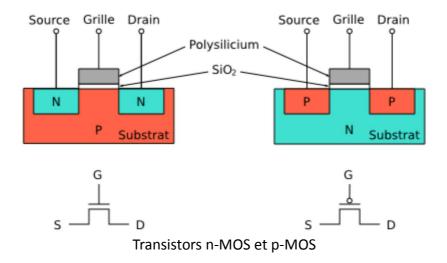

Le transistor est la *brique* avec laquelle sont construits les circuits électroniques tels les micro-processeurs. La technologie actuellement utilisée pour fabriquer les micro-processeurs est la technologie MOS (Metal-Oxide-Semiconductor). Il existe deux types de transistors MOS: les transistors de type n et les transistors de type p. Les micro-processeurs actuels utilisent des transistors des deux types. On parle alors de technologie CMOS (Complementary Metal-Oxide-Semiconductor).

#### **Fonctionnement**

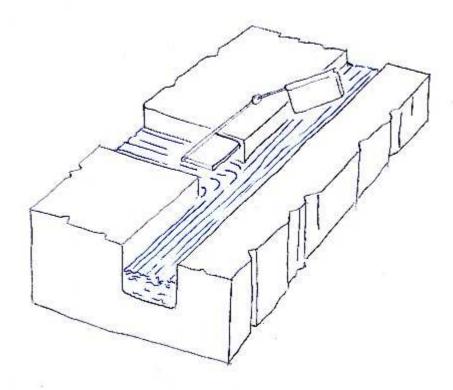

Un transistor possède trois broches appelées drain, grille et source. Pour d'autres types de transistors, elle sont aussi appelées collecteur, base et émetteur. Dans le cas des transistors MOS, le drain et la source jouent des rôles (presque) symétriques et sont (pratiquement) interchangeables. Un transistor se comporte comme un interrupteur électrique entre la source et le drain qui serait commandé par la grille. Le dessin ci-dessous illustre de manière imagée la façon dont fonctionne un transistor.

Fonctionnement imagé d'un transistor

Le comportement d'un transistor n-MOS est le suivant. Si la grille est mise à une tension de 2.9V, la source et le drain sont connectés. Si au contraire, la grille est mise à une tension de 0V, le circuit entre la source et le drain est ouvert. Le fonctionnement d'un transistor p-MOS est l'inverse. Le drain et la source sont connectés lorsque la tension appliquée à la grille est 0V.

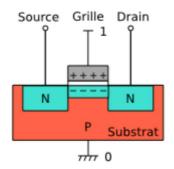

#### Composition

Un transistor est formé de deux jonctions np obtenues en intercalant une couche p (respectivement n) entre deux couches n (respectivement p). Le transistor de type n correspond aux trois couches n-p-n et le transistor de type p aux couches p-n-p. Il y a en outre une grille en métal au début de la technique MOS mais maintenant faite en polysilicium. Cette grille est séparée de la couche intermédiaire par une fine couche d'oxyde de silicium  $sio_2$  isolant. Le potentiel appliqué à la grille permet de modifier l'état de la couche intermédiaire.

#### Principe de fonctionnement

On considère un transistor de type n. Si aucune tension n'est appliquée à la grille, les deux jonctions np et pn se comporte comme des diodes en opposition et aucun courant ne peut passer entre la source et le drain. Si au contraire une tension positive est appliquée à la grille, les électrons chargés négativement s'accumulent dans le substrat dans la zone près de la grille. La région du substrat près de la grille va alors se comporter comme un semi-conducteur dopé n (cf. figure ci-dessous). Le courant peut alors passer entre la source et le drain.

Formation d'un tunnel n dans le substrat

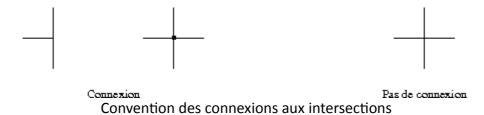

#### Conventions dans les schémas

Dans tous les schémas du cours, on adopte la convention qui est illustrée à la figure suivante. Si un fil s'arrête a une intersection avec un autre fil, les deux fils sont connectés. Si par contre, deux fils se croisent, il n'y a pas connexion des deux fils sauf si l'intersection est matérialisée par un gros point.

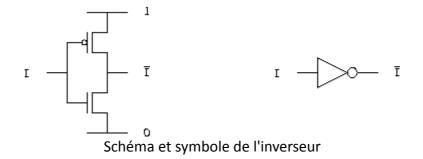

### Portes not, nand et nor

La porte la plus simple est la porte *not* de la négation. Elle prend en entrée une valeur x qui vaut 0 ou 1 et elle sort la valeur 1-x. La table de vérité de cette porte est donnée ci-dessous.

| Entrée | Sortie |

|--------|--------|

| ı      | 7      |

| 0      | 1      |

| 1      | 0      |

La porte *not* peut être réalisée en logique CMOS par un circuit constitué de deux transistors, un de type n et un de type p. Ce circuit est appelé *inverseur*. L'inverseur ainsi que son symbole sont représentés à la figure ci-dessous.

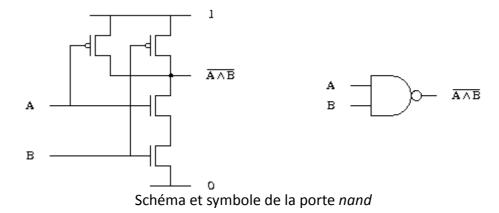

La porte *nand* prend en entrée deux valeurs 0 ou 1. La sortie vaut 0 si les deux entrées valent 1 et elle vaut 1 si au moins une des deux entrées vaut 0. La table de vérité est donnée ci-dessous.

| Entrées |   | Sortie   |

|---------|---|----------|

| Α       | В | ¬(A ∧ B) |

| 0       | 0 | 1        |

| 0       | 1 | 1        |

| 1       | 0 | 1        |

| 1 | 1 | 0 |

|---|---|---|

Un circuit pour réaliser la porte *nand* en logique CMOS est donné ci-dessous. Il est constitué de quatre transistors dont deux n-MOS et deux p-MOS.

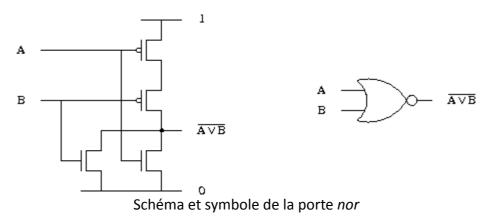

La porte *nor* prend en entrée deux valeurs 0 ou 1. La sortie vaut 0 si au moins une des entrées vaut 1 et elle vaut 1 si les deux entrées valent 0. La table de vérité est donnée ci-dessous.

| Entrées |   | Sortie   |

|---------|---|----------|

| Α       | В | ¬(A ∨ B) |

| 0       | 0 | 1        |

| 0       | 1 | 0        |

| 1       | 0 | 0        |

| 1       | 1 | 0        |

Un circuit pour réaliser la porte *nor* en logique CMOS est donné ci-dessous. Il est constitué de quatre transistors dont deux n-MOS et deux p-MOS. C'est le circuit dual du circuit de la porte *nand*. Les deux transistors p-MOS qui était en parallèle dans le circuit de la porte *nand* sont en série dans le circuit de la porte *nor*. Au contraire, les deux transistors n-MOS qui était en série dans le circuit de la porte *nand* sont en parallèle dans le circuit de la porte *nor*.

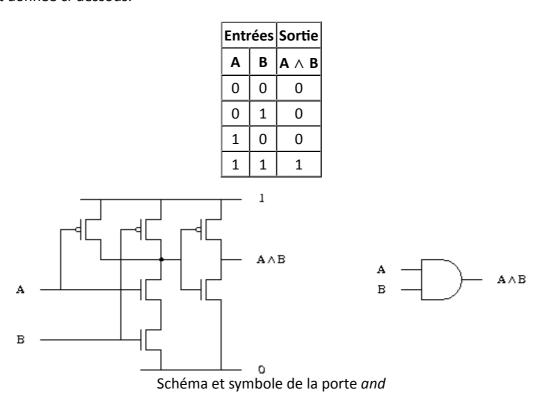

### Portes or et and

Si dans le schéma de la porte *nor*, chaque transistor n-MOS est remplacé par un transistor p-MOS et inversement, on obtient un schéma qui donne théoriquement une porte *and*. Pourtant, le circuit de la porte *and* n'est pas réalisé de cette manière. Cela provient du fait que la source et le drain des transistors ne jouent pas des rôles complètement symétriques. Pour des raisons de consommation, les connexions avec le 0 sont toujours commandées par des transistors de type n et les connexions avec le 1 par des transistors de type p.

Les circuits des portes *and* et or sont respectivement obtenus en combinant un circuit de la porte *nand* et *nor* avec un inverseur.

La porte and prend en entrée deux valeurs 0 ou 1. La sortie vaut 1 si les deux entrées valent 1 et elle vaut 0 sinon. La

table de vérité est donnée ci-dessous.

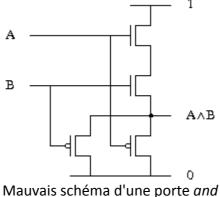

La porte and pourrait théoriquement être aussi réalisée par le schéma ci-dessous qui comporte moins de transistors. Ce schéma n'est cependant pas utilisé en pratique. Dans ce schéma, la sortie est reliée au 1 par des transistors n et au 0 par des transistors p. Ceci induit une consommation excessive par rapport au schéma précédent.

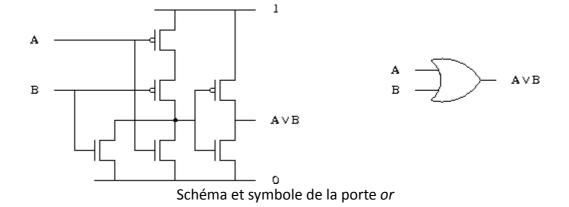

La porte or prend en entrée deux valeurs 0 ou 1. La sortie vaut 0 si les deux entrées valent 0 et elle vaut 1 sinon. La table de vérité est donnée ci-dessous.

| Entrées |   | Sortie |

|---------|---|--------|

| Α       | В | A ∨ B  |

| 0       | 0 | 0      |

| 0       | 1 | 1      |

| 1       | 0 | 1      |

| 1       | 1 | 1      |

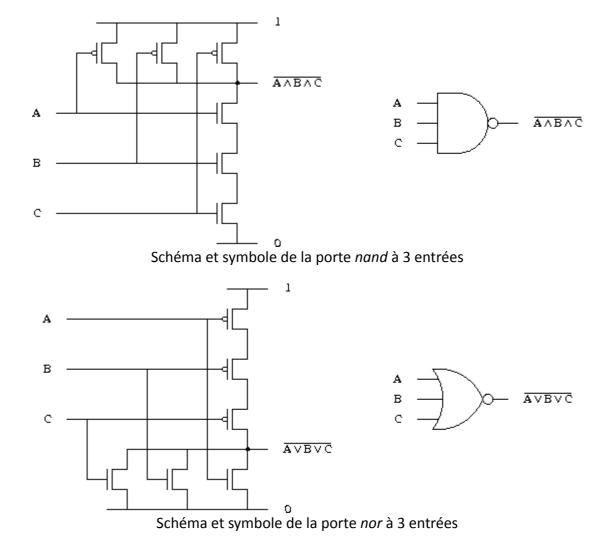

### Portes nand et nor à trois entrées

On peut bien sûr réaliser une porte *nand* à trois entrées en combinant deux portes *nand* à deux entrées. Il est plus économique en nombre de transistors de réaliser directement cette porte. C'est la même chose pour la porte *nor* à trois entrées.

## Portes and et or à entrées multiples

Les schémas des portes *nand* et *nor* à trois entrées peuvent être généralisés pour obtenir des schémas pour des portes *nand* et *nor* à un nombre quelconque d'entrées. Pour des raisons technologiques, ces portes ne sont pas réalisées de cette façon. Il est préférable de construire des portes à un grand nombre d'entrées en combinant plusieurs portes à 2 ou 3 entrées.

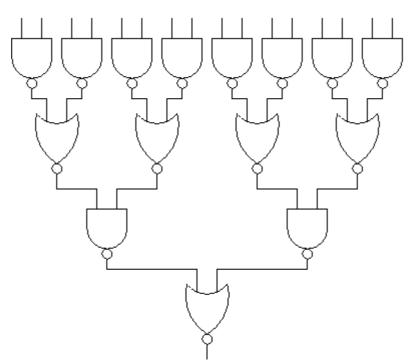

Des circuits pour les portes and ou or à entrées multiples peuvent être construits en utilisant un arbre constitué de portes and ou or respectivement. La construction d'un circuit pour une porte à k entrées peut être faite de manière récursive. Si k vaut 1 ou 2, le circuit est évident. Si k est supérieur à 2, on construit d'abord deux circuits ayant respectivement  $\lfloor k/2 \rfloor$  et  $\lceil k/2 \rceil$  entrées. Les sorties des ces deux circuits sont ensuite envoyées sur une dernière porte

and ou or. On vérifie par récurrence que le nombre de portes d'un tel circuit est exactement k-1 et que sa profondeur (nombre maximal de portes mises en cascade) est  $\lceil \log_2(k) \rceil$ .

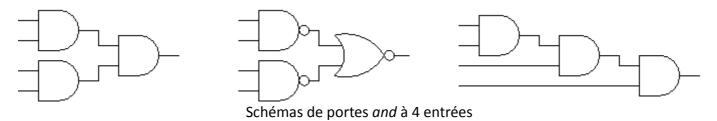

Pour k = 4, on obtient le premier circuit représenté à la figure ci-dessous. Pour économiser les transistors, chaque bloc de trois portes *and* ou *or* peut être remplacé par deux portes *nand* et une porte *nor* ou l'inverse. On obtient ainsi le second circuit représenté à la figure ci-dessous. Il existe d'autres circuits comme le troisième représenté à la figure ci-dessous qui réalisent une porte *and* à 4 entrées. Ce circuit est cependant à éviter car il augmente le temps de latence en raison de sa plus grande profondeur.

En appliquant le procédé ci-dessus pour k = 16, puis en remplaçant chaque bloc de trois portes *and* par deux portes *nand* et une porte *nor*, on obtient le circuit ci-dessous qui a 10 portes *nand* et 5 portes *nor*. Ce circuit est particulièrement régulier car k est une puissance de 2.

Schéma d'une porte and à 16 entrées

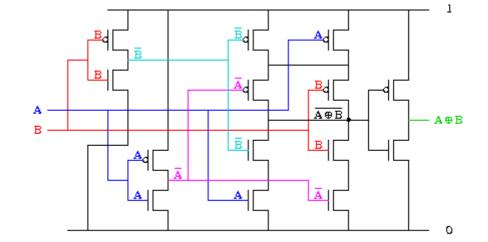

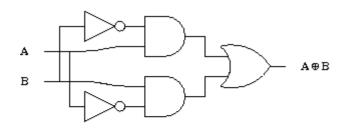

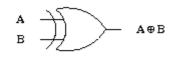

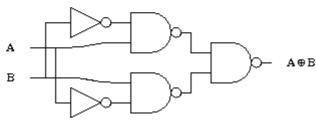

#### Porte xor

La porte xor permet de réaliser la fonction ou exclusif qui s'avère très utile pour construire les additionneurs. Comme toutes les autres fonctions booléennes, elle se réalise avec les portes and et or ou bien encore nand et nor. Il faut la considérer comme une abréviation pour un petit circuit très utile.

| Entrées |   | Sortie |

|---------|---|--------|

| Α       | В | A ⊕ B  |

| 0       | 0 | 0      |

| 0       | 1 | 1      |

| 1       | 0 | 1      |

| 1       | 1 | 0      |

Schémas et symbole de la porte *xor*